Othello

The Tragedy of Othello, the Moor of Venice, often shortened to Othello (/ɒˈθɛloʊ/), is a tragedy written by William Shakespeare around 1603. Set in Venice and Cyprus, the play depicts the Moorish military commander Othello as he is manipulated by his ensign, Iago, into suspecting his wife Desdemona of infidelity. Othello is widely considered one of Shakespeare's greatest works and is usually classified among his major tragedies alongside Macbeth, King Lear, and Hamlet. Unpublished in the author's life, the play survives in one quarto edition from 1622 and in the First Folio.

Othello has been one of Shakespeare's most popular plays, both among playgoers and literary critics, since its first performance, spawning numerous stage, screen, and operatic adaptations. Among actors, the roles of Othello, Iago, Desdemona, and Emilia (Iago's wife) are regarded as highly demanding and desirable. Critical attention has focused on the nature of the play's tragedy, its unusual mechanics, its treatment of race, and on the motivations of Iago and his relationship to Othello. Originally performed by white actors in dark makeup, the role of Othello began to be played by black actors in the 19th century.

Shakespeare's major source for the play was a novella by Cinthio, the plot of which Shakespeare borrowed and reworked substantially. Though not among Shakespeare's longest plays, it contains two of his four longest roles in Othello and Iago.

Characters

[edit]- Othello – General in the Venetian military, a noble Moor

- Desdemona – Othello's wife; daughter of Brabantio

- Iago – Othello's trusted, but jealous and traitorous ensign

- Cassio – Othello's loyal and most beloved captain

- Emilia – Iago's wife and Desdemona's maidservant

- Bianca – Cassio's lover

- Brabantio – Venetian senator and Desdemona's father (can also be called Brabanzio)

- Roderigo – dissolute Venetian, in love with Desdemona

- Duke of Venice

- Gratiano – Brabantio's brother

- Lodovico – Brabantio's kinsman and Desdemona's cousin

- Montano – Othello's Venetian predecessor in the government of Cyprus

- Clown – servant

- Senators

- Sailor

- Officers, Gentlemen, Messenger, Herald, Attendants, Musicians, etc.

Plot

[edit]

Act I

[edit]Roderigo, a wealthy and dissolute gentleman, complains to his friend Iago, an ensign, that Iago has not told him about the recent secret marriage between Desdemona, the daughter of Brabantio, a senator, and Othello, a Moorish general in the Venetian army. Roderigo is upset because he loves Desdemona and had asked her father, Brabantio, for her hand in marriage, which Brabantio denied him.

Iago hates Othello for promoting an aristocrat named Cassio above him, whom Iago considers a less capable soldier than himself. Iago tells Roderigo that he plans to exploit Othello for his own advantage and convinces Roderigo to wake Brabantio and tell him about his daughter's elopement. Meanwhile, Iago sneaks away to find Othello and warns him that Brabantio is coming for him.

Brabantio, provoked by Roderigo, is enraged and seeks to confront Othello, but he finds Othello accompanied by the Duke of Venice's guards, who prevent violence. News has arrived in Venice that the Turks are going to attack Cyprus, and Othello is therefore summoned to advise the senators. Brabantio has no option but to accompany Othello to the Duke's residence, where he accuses Othello of seducing Desdemona by witchcraft.

Othello defends himself before the Duke of Venice, Brabantio's kinsmen Lodovico and Gratiano, and various senators. Othello explains that, while he was invited to Brabantio's home, Desdemona became enamoured of him for the sad and compelling stories he told of his life before Venice, not because of any witchcraft. The senate is satisfied once Desdemona confirms that she loves Othello, but Brabantio leaves, saying that Desdemona will betray Othello: "Look to her, Moor, if thou hast eyes to see. She has deceived her father, and may thee" (Act I, Sc 3). Iago, still in the room, takes note of Brabantio's remark. By order of the Duke, Othello leaves Venice to command the Venetian armies against invading Turks on the island of Cyprus, accompanied by his new wife, his new lieutenant Cassio, his ensign Iago, and Iago's wife, Emilia, as Desdemona's attendant.

Act II

[edit]The party arrives in Cyprus to find that a storm has destroyed the Turkish fleet. Othello orders a general celebration and leaves to consummate his marriage with Desdemona. In his absence, Iago gets Cassio drunk, and then persuades Roderigo to draw Cassio into a fight. Montano tries to calm down an angry and drunk Cassio. This leads to their fighting one another and Montano's being injured. Othello arrives and questions the men as to what happened. Othello blames Cassio for the disturbance and strips him of his rank. Cassio, distraught, is then persuaded by Iago to ask Desdemona to persuade her husband to reinstate him.

Act III

[edit]Iago persuades Othello to be suspicious of Cassio and Desdemona's relationship. When Desdemona drops a handkerchief (the first gift given to her by Othello), Emilia finds it and gives it to Iago at his request, unaware of what he plans to do with it. Othello appears and, then being convinced by Iago of his wife's unfaithfulness with his captain, vows with Iago for the death of Desdemona and Cassio, after which he makes Iago his lieutenant.

Act IV

[edit]Iago plants the handkerchief in Cassio's lodgings, then tells Othello to watch Cassio's reactions while Iago questions him. Iago goads Cassio on to talk about his affair with Bianca, a local courtesan, but whispers her name so quietly that Othello believes the two men are talking about Desdemona. Later, Bianca accuses Cassio of giving her a second-hand gift which he had received from another lover. Othello sees this, and Iago convinces him that Cassio received the handkerchief from Desdemona.

Enraged and hurt, Othello resolves to kill his wife and tells Iago to kill Cassio. Othello proceeds to make Desdemona's life miserable and strikes her in front of visiting Venetian nobles. Meanwhile, Roderigo complains that he has received no results from Iago in return for his money and efforts to win Desdemona, but Iago convinces him to kill Cassio.

Act V

[edit]

Roderigo unsuccessfully attacks Cassio in the street after Cassio leaves Bianca's lodgings, as Cassio wounds Roderigo. During the scuffle, Iago comes from behind Cassio and badly cuts his leg. In the darkness, Iago manages to hide his identity, and when Lodovico and Gratiano hear Cassio's cries for help, Iago joins them. When Cassio identifies Roderigo as one of his attackers, Iago secretly stabs Roderigo to death to stop him from revealing the plot. Iago then accuses Bianca of the failed conspiracy to kill Cassio.

Othello confronts a sleeping Desdemona. She denies being unfaithful, but he smothers her. Emilia arrives, and Desdemona defends her husband before dying, and Othello accuses Desdemona of adultery. Emilia calls for help. The former governor Montano arrives with Gratiano and Iago. When Othello mentions the handkerchief as proof, Emilia realizes what Iago has done, and she exposes him. Othello, belatedly realising Desdemona's innocence, stabs Iago (but not fatally), saying that Iago is a devil, but not before the latter stabs Emilia to death in the scuffle.

Iago refuses to explain his motives, vowing to remain silent from that moment on. Lodovico apprehends both Iago and Othello for the murders of Roderigo, Emilia, and Desdemona, but Othello commits suicide. Lodovico appoints Cassio as Othello's successor and exhorts him to punish Iago justly. He then denounces Iago for his actions and leaves to tell the others what has happened.

Date and sources

[edit]Shakespeare's sources

[edit]Shakespeare's primary source for the plot was the story of a Moorish Captain (third decade, story seven) in Gli Hecatommithi by Cinthio (Giovanni Battista Giraldi), a collection of one hundred novellas about love, grouped into ten "decades" by theme.[1] The third decade deals with marital infidelity.[2] Of Cinthio's characters, only Disdemona (the equivalent of Shakespeare's Desdemona – her name means "ill-omened" in Italian) is named – the others are simply called the Moor (the equivalent of Othello), the Ensign (Iago), the Corporal (Cassio) and similar descriptions.[3][4] In its story the Ensign falls in love with the Moor's wife Disdemona, but her indifference turns his love to hate and in revenge he persuades the Moor that Disdemona has been unfaithful. The Moor and the Ensign murder Disdemona with socks filled with sand, and bring down the ceiling of her bedchamber to make it appear an accident. The story continues until the Ensign is tortured to death for unrelated reasons and the Moor is killed by Disdemona's family.[3][a]

Shakespeare's direct sources for the story do not include any threat of warfare: it seems to have been Shakespeare's innovation to set the story at the time of a threatened Turkish invasion of Cyprus – apparently fixing it in the events of 1570. Those historical events would however have been well known to Shakespeare's original audience, who would therefore have been aware that – contrary to the action of the play – the Turks took Cyprus, and still held it.[5][6]

Scholars have identified many other influences on Othello: things which are not themselves sources but whose impact on Shakespeare can be identified in the play:[7] these include Virgil's Aeneid,[8] Ovid's Metamorphoses,[9] both The Merchant's Tale and The Miller's Tale from Chaucer's The Canterbury Tales,[10] Geoffrey Fenton's Certaine Tragicall Discourses,[11][12] Kyd's The Spanish Tragedy,[13] George Peele's The Battle of Alcazar,[14][15] the anonymous Arden of Faversham,[16][17] Marlowe's Doctor Faustus,[18] and Heywood's A Woman Killed with Kindness.[19] These also include Shakespeare's own earlier plays Much Ado About Nothing, in which a similar plot was used in a comedy,[20] The Merchant of Venice with its high-born, Moorish, Prince of Morocco,[21] and Titus Andronicus, in which a Moor, Aaron, was a prominent villain, and as such was a forerunner of both Othello and Iago.[22][23]

One such influence is not a literary work at all. In 1600, London was visited for "half a year" by the Moorish ambassador of the King of Barbary, whose entourage caused a stir in the city. Shakespeare's company is known to have played at court during the time of the visit, and so would have encountered the foreign visitors at first hand.[24]

Among Shakespeare's non-fiction, or partly-fictionalised, sources were Gasparo Contarini's Commonwealth and Government of Venice[25][26] and Leo Africanus's A Geographical Historie of Africa.[27][28][29] Himself a Moor from Barbary, Leo said of his own people "they are so credulous they will beleeue matters impossible, which are told them" and "no nation in the world is so subject vnto iealousie; for they will rather [lose] their liues than put vp any disgrace in the behalfe of their women" – both traits seen in Shakespeare's Othello.[30] And from Leo's own life story Shakespeare took a well-born, educated African finding a place at the height of a white European power.[29] From Philemon Holland's translation of Pliny's Natural History Shakespeare took the references to the Pontic Sea,[31] to Arabian trees with their medicinable gum,[32] and to the "Anthropophagi and men whose heads do grow beneath their shoulders",[33][34] elements which also featured in the fantastic The Travels of Sir John Mandeville.[12][35]

Date

[edit]

The terminus ad quem for Othello (that is, the latest year in which the play could have been written) is 1604, since a performance of the play in that year is mentioned in the accounts book of Sir Edmund Tilney, then Master of the Revels.[36][37]

A terminus a quo (i.e. the earliest year in which it could have been written) is given by the fact that one of its sources, Holland's translation of Pliny's Natural History, was published in 1601.[36]

Within this range, scholars have tended to date the play 1603–1604, within the reign of James I, since the play appears to have elements designed to appeal to the new king, who had written a poem about the defeat of the Turkish navy at Lepanto, and to the new queen, Anne of Denmark, in whose circle there was an interest in the blackface exoticism also reflected in Ben Jonson's The Masque of Blackness, in which the queen and her ladies appeared as "daughters of Niger".[38] That dating is supported by similarities to Measure for Measure, another of Shakespeare's plays often dated around 1604, and which, like Othello, draws its plot from Cinthio's Gli Hecatommithi.[39] This date is also supported by the possibility that Shakespeare may have consulted Richard Knolles' 1603 The Generall Historie of the Turkes.[39]

However, evidence of an earlier date, 1601–1602, is provided by the so-called bad quarto of Shakespeare's play Hamlet, published in 1603. The theory is that the bad quarto is a memorial reconstruction of Hamlet, made by some of its actors: so where there are unintentional echoes of Othello in the bad quarto (for example "to my vnfolding / Lend thy listning eare"[40] in the bad quarto and "To my unfolding lend your prosperous ear"[41] in Othello – and a number of others) it suggests that the actors must have been performing Othello, at the latest, in the season preceding the bad quarto's publication.[42]

Early editions

[edit]

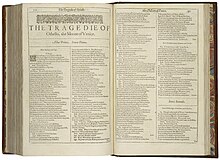

Othello was not published in Shakespeare's lifetime.[43] The first published version of the play was a quarto in 1622 (usually abbreviated to "Q"), which was followed a year later by the play's appearance in the First Folio (usually abbreviated to "F").[43]

There are significant differences between the two early editions, the most prominent of which are:

- F contains about 160 lines which are not in Q, sometimes in passages which are quite extended and well-known, such as Othello's "Pontic Sea" speech[44] and Desdemona's "Willow Song".[45][46]

- Q has fuller and more elaborate stage directions than F.[43]

- Q has 63 oaths or profanities which do not appear in F, suggesting the possibility that F was based on a manuscript which had been edited to conform with the 1606 Act of Abuses.[43][47]

- There are over a thousand variations in wording, lineation, spelling and punctuation.[43]

There is no scholarly consensus to account for the differences between Q and F:[48]

- E. K. Chambers in 1930 argued that Q derived from a scribal manuscript, and F from the author's holograph.[49]

- Alice Walker in 1952 argued that F was printed from a corrected copy of Q.[49]

- W. W. Greg in 1955 argued that Q's copy must have been a difficult-to-read transcript of Shakespeare's "foul papers" (i.e. first drafts).[50]

- M. R. Ridley in 1958, rejecting Walker's argument and accepting Greg's, argued that Q had greater authority and rejected F's changes as "memorial contamination" from a theatre prompt book or as "sophistications" by the editors of F.[51]

- Nevill Coghill in 1964 argued that the changes in F were improvements made by the author, who might have taken advantage of the need to revise the play in consequence of the Act of Abuses to make other changes.[51]

- Gary Taylor in 1983 agreed with Coghill that F incorporated the author's own improvements to Q, but argued that another scribal hand had also made intervening changes to F.[52]

- E. A. J. Honigmann in 1996 partly revived Walker's theory, by arguing that the scribe responsible for preparing the manuscript for F had consulted Q whenever the copy was illegible.[53] He also argues that sequences in F but not in Q, such as the Willow Song, may have been cuts from the original made for the manuscript of Q, rather than later additions made for the manuscript of F.[54]

As the Oxford Shakespeare editor Michael Neill summarises things: "The textual mystery of Othello is unlikely ever to be resolved to general satisfaction."[55]

Themes and critical approaches

[edit]Jealousy

[edit]"O beware, my lord, of jealousy! It is the green eyed monster, which doth mock the meat it feeds on."

Iago[56]

The influential early twentieth-century Shakespeare critic A. C. Bradley defined Othello's tragic flaw as a sexual jealousy so intense that it "converts human nature into chaos, and liberates the beast in man ... the animal in man forcing itself into his consciousness in naked grossness, and he writhing before it but powerless to deny it entrance, grasping inarticulate images of pollution, and finding relief only in a bestial thirst for blood."[57]

This jealousy is symbolized in the play through animal imagery. In the early acts of the play it is Iago who mentions ass, daws, flies, ram, jennet, guinea-hen, baboon, wild-cat, snipe, monkeys, monster and wolves. But from the third act onwards Othello catches this line of imagery from Iago as his irrational jealousy takes hold.[58] The same occurs with "diabolical" imagery (i.e. images of hell and devils) of which Iago uses 14 of his 16 diabolical images in the first two acts, yet Othello uses 25 of his 26 in the last three acts.[59]

Not only Othello, but also Iago is consumed by jealousy: his is a kind of envy, which contemporary scholar Francis Bacon called "the vilest affection, and the most depraved; for which cause, it is the proper attribute of the Devil... As it always cometh to pass, that envy worketh subtilly, and in the dark; and to the prejudice of good things."[60]

Sometimes critics have struggled to define the kind of jealousy Othello suffers, or to deny it as a motive (for example, those who claim that in Russia between 1945 and 1957 only one actor portrayed Othello as obsessed by jealousy). In fact jealousy is a wide-ranging emotion and encompasses the spectrum from lust to spiritual disillusionment within which Othello's obsession must fall. And he displays many accepted aspects of jealousy: an eagerness to snatch at proofs, indulging degrading images of the jealousy's object, snatching at ambiguities to ease the mind, dread of vulgar ridicule, and a spirit of vindictiveness.[61]

Ultimately, Othello becomes persuaded that his honour is tarnished by his wife's unfaithfulness and can only be restored through Desdemona's and Cassio's deaths.[62] And this – a code of behaviour no longer considered valid – is one reason why modern critics rarely regard Othello among Shakespeare's greatest tragedies.[63]

Race

[edit]As Ben Okri has said:

If Othello did not begin as a play about race, then its history has made it one.[64][65]

Or, as the Oxford editor Professor Michael Neill summarises it:

Anxieties about the treatment of race in Othello are a recurrent feature of both its critical and performance histories: where they once focused on the supposed scandal of miscegenation, they are nowadays more likely to address the play's complicity in racial stereotyping.[66]

In plot terms, Othello's race serves to mark him as "other".[67] As both a Christian and a black African, Othello is (as scholar Tom McAlindon puts it) both of, and not of, Venice.[68] And actor Paul Robeson considered Othello's colour as essentially secondary, as a way of emphasizing his cultural difference and consequent vulnerability in a society he does not fully understand.[69]

In the world of the play itself, Jyotsna Singh argues that Brabantio's – and others' – objection to Othello, a decorated and respected general, as a suitable husband for Desdemona, a senator's daughter, only makes sense in racist terms: reinforced by the bestial imagery used by Iago in delivering the news.[70] The racist slurs used by Iago, Roderigo and Brabantio in the play suggest that Shakespeare conceived of Othello as a black African:[71] "thicklips";[72] "an old black ram is tupping your white ewe";[73] "you'll have your daughter covered with a Barbary horse";[74] "the sooty bosom of such a thing as thou"[75] – as do things Othello says of himself: "haply for I am black";[76] or "begrimed and black as mine own face".[77][78]

There is critical divide over Othello's ethnic origin. A "Moor" broadly refers to someone from northwest Africa, especially if Muslim,[79] but in Shakespeare's England "Moor" was used with broader connotations: sometimes referring to Africans of all regions, sometimes to Arabic or Islamic peoples beyond Africa, such as those of Turkey and the Middle East, and sometimes to Muslims of any race or location.[80][81]

Racism

[edit]"I think this play is racist, and I think it is not."

Scholar Virginia Vaughan[82]

In Shakespeare's main source, Cinthio's Gli Hecatommithi, the character Disdemona (the equivalent of Shakespeare's Desdemona) says "I know not what to say of the Moor; he used to be all love towards me; but within these few days he has become another man; and much I fear that I shall prove a warning to young girls not to marry against the wishes of their parents, and that the Italian ladies may learn from me not to wed a man whose nature and habitude of life estrange from us".[83][84]

Similar wording was used in one of the earliest, and most negative, critiques of the play: Thomas Rymer writing in his 1693 A Short View of Tragedy suggested that one of the play's morals was "a caution to all Maidens of Quality how, without their Parents consent, they run away with Blackamoors."[85][86] Rymer, however, dryly observed that another such moral might be "a warning to all good Wives, that they look well to their Linnen" – as such his comments should be read within the context of his overarching criticism of the play, as unrealistic and lacking in obvious moral conclusions.

"For this noble lady, who regarded the mind more than the features of men, with a singularity rather to be admired than imitated, had chosen for the object of her affections a Moor, a black."

Othello in Tales from Shakespeare (1807) by Charles and Mary Lamb[87]

In the nineteenth century, such well-known writers as Samuel Taylor Coleridge and Charles Lamb questioned whether the play could even be called a "true tragedy" when it dramatized the inviolable taboo of a white woman in a relationship with a black man.[88] Coleridge, writing in 1818, argued that Othello could not have been conceived as black:

"Can we imagine [Shakespeare] so utterly ignorant as to make a barbarous negro plead royal birth, - at a time, too, when negroes were not known except as slaves? ... and most surely as an English audience was disposed at the beginning of the seventeenth century, it would be something monstrous to conceive this beautiful Venetian girl falling in love with a veritable negro. It would argue a disproportionateness, a want of balance, in Desdemona, which Shakespeare does not appear to have in the least contemplated."[89]

These sentiments were instrumental in ushering in the so-called "bronze age of Othello" (discussed further under "19th century" below).[90]

Martin Orkin's 1987 essay Othello and the "Plain Face" of Racism acknowledges the racist sentiments in the play; but vindicates Shakespeare who confines these views to discredited characters such as Iago, Roderigo and Brabantio.[91] He concludes that "in its fine scrutiny of the mechanisms underlying Iago's use of racism, and in its rejection of human pigmentation as a means of identifying human worth, the play, as it always has done, continues to oppose racism."[92]

The critical approach to racial issues in the play changed direction with the publication in 1996 by Howard University Press of Othello: New Essays by Black Writers edited by Mythili Kaul, which made clear that black readers and audience members may be experiencing a different play from white ones.[93] Questions about whether Othello is among Shakespeare's greatest plays are rendered irrelevant in the context of discussions about how the play illuminates the racial thinking of Shakespeare's time, and of the present day.[94]

The Nigerian poet Ben Okri in his 1997 A Way of Being Free included several "meditations" on Othello, arguing that because "it is possible that Othello actually is a blackened white man" he is not a fully formed character with a psychology but a "white myth or stereotype of black masculinity".[94] Even with that knowledge, Okri writes, "The black person's response to Othello is more secret, and much more anguished, than can be imagined. It makes you unbearably lonely to know that you can empathise with [white people], but they will rarely empathise with you. It hurts to watch Othello."[95]

From the 1980s, Othello became a role that only black actors performed.[96] However, in 1998 black actor Hugh Quarshie questioned whether the central role in Othello should be played by a black actor, saying:

"If a black actor plays a role written for a white actor does he not risk making racial stereotypes seem legitimate and even true ... does he not encourage the white way, or rather the wrong way, of looking at black men, namely that [they] are over-emotional, excitable and unstable."[97][98]

Scholar Virginia Vaughan made a related point in 2005:

"The danger of a black actor in the title role is that with the loss of the reminders that this is not real but an impersonation, the enactment of Othello's jealous rage and murder of his wife can strike audiences as the embodiment of their own stereotypes of black pathology rather than an actorly performance"[99]

Patriarchy

[edit]At Brabantio's first appearance towards the end of the first scene, he asks whether sinister "charms" may have abused "the property of youth and maidenhood" of Desdemona.[101] For him, Desdemona denying her father's right to choose her husband, and choosing a black man for herself, can only be explained by black magic.[102][103]

The notion of women as property pervades the play. Even after her death, Othello says of Desdemona: "Had she been true, / If heaven would make me such another world / Of one entire and perfect chrysolite, / I'd not have sold her for it."[104][105] Also pervasive is the male fear of female sexuality.[106]

The word "whore" appears 14 times in Othello, more often than in any other work by Shakespeare, often used (in Kay Stanton's words) as a "male-initiated inscription onto the female as scapegoat."[107] And it is one of only two of the plays (alongside Timon of Athens) in which the word "whore" is used with specific reference to every named female character.[108] In the world of the play, whorishness is understood as the true and essential nature of women – yet this is constantly shown to be a projection of male imaginations, completely unrelated to the women's perceptions of themselves or to their behavior.[109]

Towards the end of the play, Desdemona's goodness increasingly becomes represented by long-suffering martyrdom, perceived as a longstanding sign of acceptable femininity. In place of the headstrong heroine of the opening acts, Desdemona, increasingly stripped of agency, endures her husband's anger and humiliations – even his striking her in public – and eventually, while dying, tries to exonerate him for his murder of her.[110] Others perceive Desdemona's reaction as one of strength and dignity, not passivity.[111]

In contrast, Emilia ("the only real grown-up in the play", in the words of stage director Michael Attenborough[112]) revolts against misogyny, defying her husband Iago's demands three times in the final scene.[113][114]

The handkerchief

[edit]The over-reliance of the plot of Othello upon a trivial prop, the handkerchief, was noted in the play's earliest criticism. The same Thomas Rymer quoted above, in his 1693 A Short View of Tragedy, suggested that the play should better have been called "The Tragedy of the Handkerchief", arguing "the handkerchief is so remote a trifle, no booby on this side Mauritania could make any consequence from it."[115][116]

In spite of Othello's protestations in the first act that no magic was used in his wooing of Desdemona, he later claims magical properties for the handkerchief, his first gift to her.[117][118] A question which has interested critics is whether he himself believes these stories or is using them to pressure or test Desdemona.[119][120] There is certainly a contradiction between Othello's assertion – linked to its supposed magical properties – that his mother received the handkerchief from an Egyptian charmer in Act 3 Scene 4,[121] and his later assertion that his father gave it to his mother, made in Act 4 Scene 2.[122][123] Are we, the audience, intended to believe in the handkerchief's magical properties?[124]

The handkerchief provides many examples of how chance operates in support of Iago's plots: Desdemona loses it just when Iago is in need of evidence of the invented affair; Cassio fails to recognise that it is hers; Cassio gives it to Bianca to copy, who throws it back at him at the very moment when Othello is eavesdropping.[125]

Symbolically the handkerchief represents the bond between Othello and Desdemona, and its loss the breaking of that bond: Othello blames Desdemona for its loss when in fact he casts it aside while she is trying to use it to help him.[126][127] The whiteness of the handkerchief is often taken to represent Desdemona's purity; and the red strawberries blood from her hymen symbolising her virgin marriage.[128][129][130][131] In contrast, professor Ian Smith argues that a handkerchief "dyed in mummy"[132] would not be white but black, and therefore symbolic of Othello.[133]

In a 1997 production at the Royal National Theatre, the handkerchief fell to the ground immediately before the interval and remained onstage throughout it, as if – as the reviewer Richard Butler put it – "challenging one of us to pick it up and prevent a tragedy."[134]

Othello and Iago

[edit]Othello and Iago are two of the five longest parts in the Shakespeare canon. At 1097 lines, Iago's is the larger of the two: only Hamlet (in Hamlet) and Richard (in Richard III) are longer.[135]

Genre

[edit]Othello – although a tragedy – takes elements from other genres, including comedy. For example, there are similarities between Egeus' complaint about his daughter Hermia's lover Lysander, in the first Act of Shakespeare's A Midsummer Night's Dream:

With cunning hast thou filched my daughter's heart

Turned her obedience which is due to me

To stubborn harshness.[136]

And Brabantio's complaint to the Duke in Act 1 of Othello in which he asks Desdemona:

Do you perceive, in all this noble company,

Where most you owe obedience?[137][138]

Iago's motivation

[edit]The word "honest" is used more than 40 times in the play, sometimes with reference to Desdemona's chastity, but in almost all other cases with reference to Iago, where it has a double meaning – as a condescending term for a social inferior, and as a reference to his supposed truthfulness.[139]

Iago's role is (in Robert Watson's words) "overdetermined in renaissance dramatic convention": he is partly the scheming Machiavel of Renaissance tragedy, partly the vengeful malcontent of revenge tragedy, partly the instigator of jealousy in domestic tragedy and partly the devil incarnate of morality plays.[140]

The character's own motives are never made clear, because Iago himself expresses too many motives:[141]

- He hates the Moor: often with reference to Othello's race.[142][143][144]

- He is angry that Cassio has been promoted to Lieutenant, over himself.[145][146]

- He suspects Othello of having slept with Emilia.[147][146][148]

- He suspects Cassio of having slept with Emilia.[149][150]

- He himself is in love with Desdemona.[151][144]

- He envies Cassio's virtues.[152][153]

These led Samuel Taylor Coleridge to refer to Iago's "motive-hunting of motive-less Malignity".[154]

Some critics have suggested other motives: psychologist Ernest Jones's suggestion that Iago may be motivated by a repressed homosexual desire for Othello has been influential in subsequent performances of the role.[155]

As Robert Watson summarises it: "The seemingly endless critical debate about Iago's motivation reflects a truth, rather than a confusion, about the play. ... If it is disturbing to suspect that a devil may be lurking around us in human form, perhaps within our most trusted friend, it is even more disturbing to realize that this devil may be ... a reflection of our own destructive tendencies."[156]

Ultimately Iago provides no answer – refusing, at the end of the play, to reveal his motive: "Demand me nothing. What you know, you know. From this time forth I never will speak word."[157][158]

Double time scheme

[edit]Othello has a double time scheme – meaning that the timeframe of the play does not contain enough time for its action.[159] Its action is continuous from Othello and Desdemona's wedding night, except for the voyage from Venice to Cyprus (during which Cassio and Desdemona are not together) and the time in Cyprus covers an estimated 33 hours.[160] Yet this short timeframe does not allow any time for the supposed affair between Desdemona and Cassio to have happened.[161] In support of the short time scheme is the continuous nature of the action: the fleet arrives in Cyprus in the afternoon and the plot against Cassio proceeds that evening into the early morning; Cassio resolves to seek Desdemona's help the following morning, and does so, commencing the long "temptation scene"[b] by the end of which Othello has resolved to kill Desdemona and has ordered Iago to attempt to kill Cassio, all of which happens that same night.[162] And this urgency is underlined by the text: in particular's Iago's concern that if Othello compares notes with anyone else it will become clear that Iago is playing one character against another.[160][c]

But there is also a long time scheme. Iago persuades Othello that Desdemona and Cassio have "the act of shame a thousand times committed";[163] Emilia says Iago "hath a hundred times"[164] asked her to steal the handkerchief; Bianca complains Cassio has been away from her "a week";[165] news of the Turkish defeat needs time to reach Venice then Lodovico needs time to reach Cyprus;[166] and by Act 4 Roderigo (who sold all his land at the end of Act 1)[167] has already squandered all his money.[168][169]

Shakespeare's source story in Cinthio takes place entirely in the long time scheme: Shakespeare appears to have introduced the shorter time scheme to increase dramatic tension, while also introducing moments where Iago's plot could fall apart – for example if Emilia had given an honest answer to Desdemona's "Where should I lose that handkerchief?"[170] or if Roderigo had chosen to denounce Iago.[169]

The discovery of a double time scheme has been ascribed to articles written by John Wilson in Blackwood's Magazine in 1849 and 1850, although references to the problem predate that.[171] The whole question is sometimes rejected as "academic nit-picking".[171] (Director Michael Attenborough, asked about it in an interview, replied "I strongly suspect Shakespeare didn't think about it very much."[172]) And as Michael Neill points out, many of the problems disappear if one supposes that Othello believed Cassio and Desdemona's affair had commenced prior to Othello and Desdemona's elopement.[173] Neill summarises the issue as "no more than a particularly striking side-effect of the general indifference to naturalistic handling of time and space that Shakespeare shared with other dramatists of the period."[174]

Performance history

[edit]

Shakespeare's day to the Interregnum

[edit]Othello was written for and performed by the King's Men, the playing company to which Shakespeare belonged, and the 1622 Quarto notes on its title page that the play was "Diuerse times acted at the Globe, and at Black-Friers, by his Maiesties seruants".[175] These two theatres had very different features – the former a large outdoor theatre accommodating an audience of 3,000; the latter a private indoor theatre that sat around 700, paying higher prices – and the style of playing would have adapted to these different conditions.[175] The play was performed at Court by the King's Men on 1 November 1604, and again in 1612-13 as part of the celebrations for the Wedding of Princess Elizabeth and Frederick V of the Palatinate.[175]

The title role was originally played by Richard Burbage, whose eulogies reveal that he was admired in the role.[176][177] Moorish characters were conventionally played in turbans, with long white gowns and red trousers, with the actor's face darkened with lampblack or coal.[178] The original Iago was likely John Lowin.[179][180]

Restoration and 18th century

[edit]All theatres were closed down by the Puritan government on 6 September 1642. Upon the restoration of the monarchy in 1660, two patent companies (the King's Company and the Duke's Company) were established, and the existing theatrical repertoire divided between them: Othello being allocated to the King's Company's repertoire.[181] These patents stated that "all the women's parts to be acted in either of the said two companies for the time to come may be performed by women". The first professional acting appearance by a woman on the English stage was that of Desdemona in Othello on 8 December 1660, although history does not record who took the role.[182][183] Margaret Hughes is the first woman known to have played Desdemona.[184]

In Restoration theatres, it was common for Shakespeare's plays to be adapted or rewritten.[185] Othello was not adapted in this way, although it has often been cut to conform to current ideas of decorum or refinement.[186] These cuts were not limited to removing violent, religious or sexual content, but extended on different occasions to removing references to eavesdropping, to Othello's fit, to Othello's tears, to the first 200 lines of the fourth act, or to the entire role of Bianca.[187]

Among seventeenth- and eighteenth-century actors praised for expressing the nobility of the Moor – and fully exploring the degrading passions which lead to the brutal murder he commits – were Thomas Betterton and Spranger Barry.[188] A review of the latter by John Bernard expressed how Barry's Othello "looked a few seconds in Desdemona's face, as if to read her feelings and disprove his suspicions; then, turning away, as the adverse conviction gathered in his heart, he spoke falteringly, and gushed into tears."[189]

The first professional performances of the play in North America are likely to have been those of the Hallam Company: Robert Upton (William Hallam's advance man) performed Othello at a makeshift theatre in New York on 26 December 1751; and religious objections to theatre led the Hallam Company to perform Othello as a series of "moral dialogues" at Rhode Island in 1761.[190]

Although not performed in Portugal until the nineteenth century, the play holds of the distinction of being the first of Shakespeare's works to have reached a Portuguese-speaking country, possibly at the request of a Portuguese reader, in 1765.[191]

19th century

[edit]Paul Robeson's iconic performance (see 20th Century, below) was not the first professional performance of the title role by a black actor: the first known is James Hewlett at the African Grove Theatre, New York, in 1822.[192] And Hewlett's protégé Ira Aldridge (billed as "The African Roscius") played many Shakespearean roles across Europe for forty years, including Othello at the Royalty Theatre, London, in 1825.[193]

There are stories of extravagant audience reactions to the play. One of the most extreme is related by French novelist Stendhal who reports that at the Baltimore Theatre in 1822 a soldier interrupted the performance just before Desdemona's murder, shouting "It will never be said that in my presence a confounded Negro has killed a white woman!" The soldier fired his gun, breaking the arm of the actor playing Othello.[194]

Throughout the eighteenth and nineteenth centuries, Othello was regarded as the most demanding of Shakespeare's roles: it is considered a part of theatre legend that Edmund Kean collapsed while playing the role, and died two months after.[195] Leigh Hunt saw Kean's Othello in 1819, describing his performance in The Examiner as "the masterpiece of the living stage".[196] Before Kean, the leading exponent of the role had been John Philip Kemble who played a "neoclassical hero". In contrast, Kean presented Othello as a man of romantic temperament, and uncontrollable passion.[197] It was also Kean who initiated the so-called "Bronze Age of Othello" by insisting that "it was a gross error to make Othello either a negro or a black"[198] and thereby commencing a stage tradition of using lighter makeup rather than blackface.[199] An advantage of this change was that the actor's facial expressions could be more clearly seen.[200]

Critics have naturally focused on the two central male roles. But Emilia becomes a powerful role in the final act. Indeed Charlotte Cushman's Emilia was said to upstage Edwin Forrest's Othello in 1845.[201] And when Fanny Kemble played Desdemona in 1848 she changed the performance tradition. Previously, Desdemonas had (in her words) "always appeared to me to acquiesce with wonderful equanimity in their assassination" but Kemble, a passionate feminist and abolitionist, decided "I shall make a desperate fight for it, for I feel horribly at the idea of being murdered in my bed."[202]

In 1848, Othello was produced by Barry Lewis at the Sans Souci Theatre in Calcutta. The casting of the white "Mrs. Anderson" opposite the dark-skinned Indian Baishnav Charan Auddy led to controversy, to polarized reviews, and to a fiasco on the opening night when half of the cast, military men, were prohibited from leaving barracks by order of the Brigadier of Dum Dum.[203]

For Tommaso Salvini and Edwin Booth the role of Othello was a career-length project.[204] Salvini always played the role in Italian, even when acting alongside a company performing in English.[205] His conception of the role was of a barbarian with savage and passionate instincts concealed by a thick veneer of civilisation.[206] Konstantin Stanislavski admired, and was greatly influenced by, Salvini's Othello, which he saw in 1882. In My Life in Art, Stanislavski recalls Salvini's scene before the Senate, saying that the actor "grasped all of us in his palm, and held us there as if we were ants or flies".[207] Booth, in complete contrast, played Othello as a restrained gentleman. When Ellen Terry played Desdemona she commented on how much Booth's style helped her: "It is difficult to preserve the simple, heroic blindness of Desdemona to the fact that her lord mistrusts her, if her lord is raving and stamping under her nose. Booth was gentle with Desdemona."[208]

Booth was also an acclaimed Iago, and his advice to actors of the role was: "to portray Iago properly you must seem to be what all the characters think and say you are, not what the spectators know you to be; try to win even them by your sincerity. Don't act the villain."[209]

Stanislavski himself first played Othello in 1896. He was dissatisfied with his own performance, later recalling "I was able to reach nothing more than insane strain, spiritual and physical impotence, and the squeezing of tragic emotion out of myself."[210]

20th century

[edit]

Othello was performed in the Shimpa style in Japan in 1903 by Otojiro Kawakami, resetting the location Cyprus to Taiwan, which was then a Japanese colony.[211]

In 1930 Stanislavski directed a production of Othello for the Moscow Art Theatre, which was influential in the development of his system. The performance was directed remotely, by letter, while Stanislavski recovered from illness in France.[212]

The most significant theatre production in wartime America featured Paul Robeson as Othello.[213] Robeson had previously played the role in London in 1930 with a cast including Peggy Ashcroft, Sybil Thorndike and Ralph Richardson, and would later take the role for the RSC in 1959 at Stratford-Upon-Avon.[214] Margaret Webster's 1943 Broadway production was considered a theatrical landmark, with Robeson (in the words of Howard Barnes) "making the Moor the great and terrible figure of tragedy which he has so rarely been on the stage."[215] José Ferrer played Iago and Uta Hagen Desdemona. Taking the Broadway run with its subsequent tour, the show was seen by over half a million people.[216] Earle Hyman saw the production numerous times when he was 17 and later recalled "this tremendous excitement - the first African-American onstage to be playing this role ... to all the blacks, he represented us. It was a moment of great pride."[217]

In 1947, Kenneth Tynan saw Frederick Valk and Donald Wolfit play Othello and Iago respectively, and described the experience as equivalent to witnessing the Chicago Fire, the Quetta Earthquake or the Hiroshima Bomb.[218]

"Black all over my body, Max Factor 2880, then a lighter brown, then Negro Number 2, a stronger brown. Brown on black to give a rich mahogany. Then the great trick: that glorious half yard of chiffon with which I polished myself all over until I shone... The lips blueberry, the tight curled wig, the white of the eyes, whiter than ever, and the black, black sheen that covered my flesh and bones, glistening in the dressing-room lights."

Laurence Olivier's makeup routine for Othello[219]

When Laurence Olivier performed Othello at the National in 1964,[220] his sense of "being black", in his words, required him "to be beautiful" with a voice "dark violet - velvet stuff" and a walk "like a soft black leopard".[221] (The filmed version of this production is discussed under "Screen" below.)

The play was extremely popular in Ethiopia, running for three years in the mid-1980s at the City Hall Theatre, Addis Ababa, in Tsegaye Gabre-Medhin's translation – performed in a static and declamatory style.[222] When Janet Suzman directed the play in South Africa during Apartheid in 1988, the performance was passionately politicised, with the racism of several characters – and especially Iago (modelled on Eugène Terre'Blanche) – foregrounded.[223] The play was highly controversial – the physical contact between the black John Kani and the white Joanna Weinburg provoking walk-outs and a pile-up of hate mail.[224]

White actors continued to dominate the role until the 1980s.[220] Willard White in 1989 was the first black actor to play Othello at Stratford since Paul Robeson thirty years earlier.[225]

A "singular and idiosyncratic"[226] performance of a white actor in the central role was Jude Kelly's "photonegative" production for the Shakespeare Theatre Company in Washington, D.C. in 1997, in which Patrick Stewart played Othello as white, while almost all other speaking parts were played by actors of African descent.[227] The script remained unchanged as regards the character's race, so the white Othello was, throughout, referred to as black.[228]

21st century

[edit]At the turn of the century, performances at the RSC were dominated by their Iagos. Richard McCabe followed Simon Russell Beale in portraying misogynistic, embittered NCOs, older than their respective Othellos:[229]

Singaporean director Ong Keng Sen produced an intercultural version of the play in 2000: his Desdemona featured actors, musicians, designers and artists from India, Korea, Myanmar, Indonesia and Singapore, performing in a range of different traditional Asian styles.[230]

Cathy Downes' 2001 production at the Court Theatre in Christchurch, New Zealand made effective use of a trope (which had had racist overtones when used by earlier European directors) of Othello reverting to his native culture: setting the action in the Waikato Land Wars, Othello was a British-adopted general leading forces against his own people, until finally bursting into a "terrifying wero" (a warrior's challenge) before exacting his revenge on Desdemona.[231]

A radically different approach was taken in Jette Steckel's 2009 German language production for the Deutsches Theater Berlin. Although the translation consistently used the word "Schwarze" for "Moor" in the original, Othello was played by the white German actress Susanne Wolff in a range of different costumes and disguises, including a gorilla suit for part of Act 4 – creating a performance in which everything is (in Ayanna Thompson's words) "conveyed through representational metaphors which render Othello's race less of a stable physical marker and more of a fractured and performative one."[232]

A common theme of modern productions of the play is an emphasis on military life. When Adrian Lester played the role in Nicholas Hytner's 2013 National Theatre production, a retired army veteran was employed to teach the cast about ranks, comportment and off-duty behaviours.[233] Another 21st century trend exemplified by that performance is to reduce the focus of the play on Othello's race by having other parts played by actors of colour also.[234] And a third is an increasing focus on Desdemona's youth and innocence, at the expense of her strength of character.[235]

In 21st century productions, more emphasis has been given to the theme of domestic violence.[236][237]

Othello's "difference" has been tested in ways other than race. A rare example is Stein Winge's 2015 casting of a white American actor, Bill Pullman, as an American Navy man adrift in Norway.[238]

The play has provided opportunities for breakout roles for rising black stars, such as Chiwetel Ejiofor who played Othello at the Donmar Warehouse in 2008, and for a change of direction for other established stars: Willard White (see "20th century", above) was better known as an opera singer and Lenny Henry (see "True Identity" under "Screen" below), who played Othello for Northern Broadsides in 2009, was better known as a stand-up comedian.[239]

When Antony Sher played Iago for the RSC,[when?] the final moment of the play, before a snap blackout, was for him to look up and stare at the audience. Director Greg Doran intended this to be strange, enigmatic, open to interpretation. But Sher later wrote that he was always clear about it: in his head the question which always rang out was:

"You saw what was happening - why didn't you stop it?"[240]

Screen

[edit]Othello has influenced many film makers, and often the results are adaptations, rather than performances of Shakespeare's text. The UK's National Film and Television Archive holds over 25 20th-Century films containing performances, adaptations or extracts from Othello including Anson Dyer's 1920 animated Othello, 1921's Carnival and its 1932 remake, the 1922 German film Othello, the 1936 Men Are Not Gods, 1941's East of Piccadilly, George Cukor's 1947 A Double Life, Orson Welles in Return to Glennascaul and Welles' own Othello, Sergei Yutkevich's Russian language Othello discussed below, two productions for BBC Television (including Jonathan Miller's for the BBC Television Shakespeare series, discussed below), Basil Dearden's All Night Long, a 1988 South African TV screening of Janet Suzman's Othello, a film of Trevor Nunn's RSC production with Willard White and Ian McKellen in the central roles, and True Identity – a crime caper in which Lenny Henry's character Miles lands the role of understudy to James Earl Jones (playing himself) in a production of Othello.[241] Carnival, Men Are Not Gods and A Double Life all feature the plot of an actor playing the title role in Shakespeare's Othello developing murderous jealousy for their Desdemonas.[242][243] This plot is also shared by the very first Othello-influenced film: the 18-minute Danish 1911 Desdemona.[244][245] All Night Long reframes the story in a jazz milieu.[246] And Richard Eyre's Stage Beauty depicts a restoration performance of the play.[247]

The filming of Orson Welles' Othello was plagued by chaos. A pattern emerged where Welles would collect his cast and crew for filming, then after four or five weeks his money would run out and filming would cease: Welles would then appear in another movie, and using his acting fee would reconvene filming. Scenes in the final movie were sometimes spliced together from one actor filmed in Italy in one year, and another actor filmed in Morocco the next.[248] Welles uses shadows, extreme camera angles and discordant piano music to force the audience to feel Othello's disorientated view of Desdemona.[249] Cages, grilles and bars are frequent images.[250] And the text is heavily cut: Othello's first words are his speech to the Senators from Act 1 Scene 3.[251][252] The film was critically panned on its 1955 release (headlines included "Mr Welles Murders Shakespeare in the Dark" and "The Boor of Venice") but was acclaimed as a classic upon its re-release in a restored version in 1992.[253]

Sergei Yutkevich's Russian film, with a screenplay by Boris Pasternak, was an attempt to make Shakespeare accessible to "the working man".[254] Yutkevitch had begun his career as a painter and then as a set designer, and his film was widely praised for its pictorial beauty.[254] The director saw his film as an opposite of Welles': where Welles began his film with a sequence from the end of the story, highlighting fate, Yutkevitch began with his Othello's back-story, thereby highlighting his characters' free will.[255]

Laurence Olivier said that the role of Othello demanded "enormously big"[256] acting, and he incorporated what The Spectator described as his "outsize, elaborate, overwhelming"[257] performance into the film of his National Theatre production. The effect to modern audiences is (in the words of Daniel Rosenthal) "laughably over-the-top"[258] – in keeping with its nature as a filmed stage performance, rather than a performance designed for the screen. The film was a financial success, and earned Oscar nominations for each of Olivier as Othello, Maggie Smith as Desdemona, Frank Finlay as Iago and Joyce Redman as Emilia.[259] Subsequent critics have been less sympathetic to Olivier's performance than his contemporary audience had been, tending to read it as racist.[260] As Barbara Hodgdon expresses it: "Oliver's Othello confirms an absolute fidelity to white stereotypes of blackness."[261]

The last of the screen versions to portray Othello in blackface was Jonathan Miller's for the BBC Television Shakespeare series, with Anthony Hopkins in the title role. Miller is said to have commented that "the play is about jealousy, not race."[262] The TV film of Willard White's performance as Othello (discussed under 20th Century performances above) has been described by Carol Chillington Rutter as "The one [screen] Othello where the women's stories get fully told",[263] particularly praising the dynamic between Imogen Stubbs' Desdemona and Zoë Wanamaker's Emilia.[264]

Oliver Parker's 1995 Othello was trailed as an "erotic thriller", including a ritualized love scene between Othello and Desdemona, and, most memorably, Othello's jealous fantasies of encounters between Desdemona and Cassio.[265][266] Swiss actress Irène Jacob as Desdemona struggled with the verse, as did Laurence Fishburne, more experienced in expletive-ridden thriller roles, as Othello.[267] Iago was Kenneth Branagh in his first outing as a screen villain.[268] The overall effect was to create, in Douglas Brode's words "the tragedy of Iago" – a performance in which Iago's dominance is such that Othello is a foil to him, not the other way around.[269] The film was described as a "fair stab at turning the Bard into a decent night at the multiplex"[270] but failed to achieve success at the box office.[268]

Other adaptations of Shakespeare's story to be filmed include Franco Zeffirelli's 1986 film of Verdi's Otello[271] and the 1956 Jubal which resets the story as a Western, centered on the Cassio character.[272] The play was abridged to 30 minutes by Leon Garfield, and produced with cel animation for the TV series Shakespeare: The Animated Tales.[273] Tim Blake Nelson's basketball-themed teen drama O reset the story at an elite boarding school. The similarity of the film's ending to the Columbine massacre, which happened while the film was being edited, delayed its release for over two years, until August 2001.[274] A British TV adaptation by Andrew Davies, screened in 2001, re-set the story among senior officers of the Metropolitan Police.[275] And the first decade of the 21st-Century saw two non-English language film adaptations: Alexander Abela's French Souli set the story in a modern-day Madagascan fishing village, and Vishal Bhardwaj's Hindi Omkara amidst political violence in modern Uttar Pradesh.[276] The 1997 Malayalam movie Kaliyattam is an adaptation set against the backdrop of Theyyam artform of Kerala.[277] The 2024 Bengali movie Athhoi is an adaptation set against a fictional town of Vinsura in West Bengal.[278]

Other media

[edit]Stage adaptations

[edit]Adaptations of – or borrowings from – Shakespeare's Othello began shortly after it first appeared, including Middleton & Rowley's 1622 The Changeling, John Ford's 1632 Love's Sacrifice, Thomas Porter's 1662 The Villain and Henry Nevil Payne's 1673 The Fatal Jealousy.[279] Edward Young's 1721 play The Revenge reversed the racial roles, featuring the "swagger part" of a black villain called Zanga whose victim was a white man.[280]

Voltaire's 1732 French play Zaïre was a "neoclassical refurbishment" of Shakespeare's "barbarous" work.[279] And across continental Europe through most of the eighteenth and nineteenth centuries the play was better known than Shakespeare's in Jean-François Ducis' adaptation and its subsequent translations, in which a heroine renamed Hédelmone is stabbed to death by Othello.[281]

Part of the explosion of the Romantic movement in France was a fashion for re-writing English plays as melodrama, including Alfred de Vigny's 1829 Othello adaptation Le More de Venise.[282]

After the Restoration, London Theatres other than the patent companies got around the illegality of performing Shakespeare by allusion and parody, such as Charles Westmacott's Othello The Moor of Fleet Street at the Adelphi in 1833.[283]

In the 19th-Century United States, Othello was often used in parody, sometimes allied with minstrel shows: with the contrast between Shakespearean verse and African-American dialect a source of racist humour.[284] Indeed, racist parodies were common in the aftermath of the abolition of the slave trade in the UK and, later, in the US: for example Maurice Dowling's 1834 Othello Travestie, George W H Griffin's 1870 Othello (Ethiopian Burlesque), the anonymous Desdemonum An Ethiopian Burlesque of 1874 and the anonymous Dar's de Money (Othello Burlesque) of 1880.[285][286]

The Black Arts Movement appropriated Othello in an entirely different vein. Amiri Baraka's twinned 1964 plays Dutchman and Slave are said to "represent the ultimate African American revision of Othello",[287] especially in Dutchman's murder of Clay, a black man, by Lulu, a white woman.[288]

The Othello story became the rock opera Catch My Soul in 1968, depicting Othello as a charismatic religious cult leader, Desdemona as a naive convert, and Iago as a malcontent cult member who thinks himself to be Satan.[289][290] In Murray Carlin's 1969 Not Now Sweet Desdemona the protagonist says of Shakespeare's play that it was "the first play of the Age of Imperialism ... Othello is about colour and nothing but colour."[291] Charles Marowitz's 1974 An Othello reworked the play in the context of the Black Power movement.[292] C. Bernard Jackson's 1979 Iago made Iago himself a Moor and a victim of racism.[293] And Caleen Sinnette Jennings' 1999 Casting Othello is a metadrama about a performance of Shakespeare's play, and the racial tensions it evokes.[294]

Roysten Abel's Othello - A Play in Black and White is set among a group of Indian actors rehearsing a Kathakali version of Othello whose own story begins to mirror the play's plot: with Iago's seduction of Othello played as a guru-disciple relationship.[295]

Among feminist appropriations of the Othello story, Paula Vogel's 1994 Desdemona, A Play about a Handkerchief sets the story in a kitchen in Cyprus, where only Desdemona, Emilia and Bianca appear.[296] In Djanet Sears' 1998 Harlem Duet, Othello's lover challenges his subservient passion: "...why you trying to please her? ... I'm so tired of pleasing White folks."[297] And Toni Morrison and Rokia Traoré's 2012 Desdemona sets its story in a timeless afterlife of the characters, in which Othello and Desdemona have leisure to talk through all facets of their relationship, and in which Desdemona is reunited with her former maid Barbary, whose actual name is Sa'ran.[298]

Othello is parodied in the form of a rap song in the stage show The Complete Works of William Shakespeare (Abridged).[299] In 2012, the Q Brothers debuted Othello: The Remix, a 90-minute hip-hop version of Othello that was part of the Globe to Globe Festival and World Shakespeare Festival.[300] It was one of the few sold-out shows during the festival and went on to have several successful international tours.[301]

Audio

[edit]One of the first full-length plays to be released on vinyl was the Broadway production starring Paul Robeson, José Ferrer and Uta Hagen, issued in 1944.[302] Othello has been performed on at least twelve separate occasions on BBC Radio.[303]

Music

[edit]The Willow Song, sung by Desdemona in Act 4 Scene 3,[304] is not an original creation of Shakespeare's, but was already a well-known ballad. As such it has surviving arrangements from both before and after Shakespeare's time.[305] The version of it thought to be most authentic, because it closely matches the lyric given by Shakespeare, is known as "The Poore Soule Sate Sighing"[306] and is one of the most performed pieces of early modern English music.[307]

The two other songs sung in the play are the drinking songs in Act 2 Scene 3.[308] The first of these, "And Let Me The Cannikin Clink", has no surviving arrangement, although it fits to several extant popular tunes.[309] The other, "King Stephen Was a Worthy Peer", is the seventh of the eight stanzas of the existing ballad "Take Thy Old Cloak About Thee".[310]

The play has been a popular source for opera. Rossini's 1816 Otello, ossia il Moro di Venezia made Desdemona its focus, and was followed by numerous translations and adaptations, including one with a happy ending.[311] But the most notable version, considered a masterpiece with a power equivalent to that of the play, is Verdi's 1887 Otello,[312] for which Arrigo Boito's libretto marked a return to faithfulness to the original plot, including the reappearance of the pillow as the murder weapon, rather than Ducis' dagger.[313]

Othello was, with Antony and Cleopatra, one of the two plays which most influenced Duke Ellington and Billy Strayhorn's jazz suite Such Sweet Thunder. Its opening track (itself titled Such Sweet Thunder, a quotation from Shakespeare's A Midsummer Night's Dream)[314] came to stand for Othello telling his tales of travel and adventure to Desdemona, as reported in the play's first act.[315][316]

Sometimes the order of the play influencing a composer is reversed, as in the appropriations of classical music by filmmakers retelling Othello's story: for example in the film O, in which excerpts from Verdi's Otello are used as a theme for Odin (the Othello character) while modern rap and hip-hop are more associated with the white college students around him.[317]

Bob Dylan's song Po' Boy features lyrics in which Desdemona turns the tables on Othello, borrowing the idea of using poisoned wine from the final act of Hamlet.[318]

Literature

[edit]Aphra Behn's 1688 novel Oroonoko, and its subsequent dramatisation by Thomas Southerne, reset Othello's enslavement in the context of the then-current Atlantic triangle.[280]

In addition to his theatrical performances noted above, the play was also central to Konstantin Stanislavski's writings, and to the development of his "system". In particular, the part of Othello is a main subject of his book Creating a Role.[319] In it, the characters of Tortzov, the director, and Kostya, the young actor – both partly autobiographical – rehearse the role of Othello in the opening act.[320]

A plot-line in Farrukh Dhondy's novel Black Swan involves the central character Lazarus, a freed slave, travelling to London in the time of Shakespeare and authoring many of the plays attributed to Shakespeare, including Othello, in a production of which Lazarus plays the title character, and kills himself.[321] The narrative voice of Caryl Phillips 1997 novel The Nature of Blood harangues Othello as a sexual and political sell-out.[292] And in Sudanese novelist Tayeb Salih's retelling of the Othello story, Season of Migration to the North, the central character Mustafa Sa'eed, on trial for the murder of his white mistress, refuses to be judged by the standards of the play, declaring:

"Othello was a lie."[322]

Notes and references

[edit]- Notes

- ^ The complete novella appears, in different translations, in Honigmann & Thompson 2016, pp. 377–396 and in Neill 2008, pp. 434–444

- ^ "The temptation scene" is a term often used in the critical literature to mean Othello 3.3.

- ^ For example Othello 5.1.20-21.

- References

- Except where otherwise stated, references to the play Othello are to Honigmann, E. A. J.; Thompson, Ayanna, eds. (2016). Othello. The Arden Shakespeare (3rd series revised ed.). Bloomsbury Publishing. ISBN 9781472571762..

- Except where otherwise stated, references to other works by Shakespeare are to Wells, Stanley; Taylor, Gary, eds. (2005). William Shakespeare: The Complete Works. The Oxford Shakespeare (second ed.). Oxford University Press. ISBN 9780199267170..

- ^ Honigmann & Thompson 2016, pp. 13, 376–377.

- ^ Honigmann & Thompson 2016, p. 13.

- ^ a b Honigmann & Thompson 2016, pp. 13–14.

- ^ Honigmann 1997, pp. 12–13.

- ^ Muir & McAlindon 2015, pp. lvii–lviii.

- ^ Bate & Rasmussen 2009, p. 7.

- ^ Neill 2008, pp. 16–17.

- ^ Enterline, Lynn "Eloquent Barbarians: Othello and the Critical Potential of Passionate Character" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.149-175 at p.158.

- ^ Enterline, 2014, p.163.

- ^ Honigmann & Thompson 2016, p. 11.

- ^ Muir 1996, p. 11.

- ^ a b Neill 2008, p. 20.

- ^ Muir & McAlindon 2015, p. xxiv.

- ^ Honigmann & Thompson 2016, p. 18.

- ^ a b Bate & Rasmussen 2009, p. 3.

- ^ Honigmann & Thompson 2016, p. 397.

- ^ Lockwood, Tom (ed.), White, Martin (ed.) "Arden of Faversham", New Mermaids edition, Methuen Drama, 2007, p.vii.

- ^ Neill 2008, p. 17.

- ^ Honigmann & Thompson 2016, p. 355.

- ^ Muir 1996, p. 8.

- ^ Honigmann & Thompson 2016, pp. 20–21.

- ^ Neill 2008, p. 18.

- ^ Honigmann & Thompson 2016, pp. 8, 20, 397.

- ^ Honigmann 1997, p. 2.

- ^ Siemon, James "Making Ambition Virtue" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.177-202 at p.178 and p.198n.

- ^ Honigmann & Thompson 2016, pp. 17–18.

- ^ Honigmann 1997, p. 4.

- ^ Neill 2008, p. 19.

- ^ a b Honigmann & Thompson 2016, p. 15.

- ^ Honigmann 1997, p. 4, citing John Pory's 1600 translation of Leo Africanus's A Geographical Historie of Africa

- ^ Othello 3.3.456.

- ^ Othello 5.2.348-349.

- ^ Othello 1.3.145-146.

- ^ Neill 2008, pp. 19–20.

- ^ Honigmann & Thompson 2016, p. 17.

- ^ a b Neill 2008, p. 339.

- ^ Honigmann & Thompson 2016, p. 349.

- ^ Neill 2008, pp. 399–400.

- ^ a b Neill 2008, p. 400.

- ^ Hamlet Q1, scene 5 lines 7-8 in Thompson, Ann and Taylor, Neil (eds.) and Shakespeare, William "Hamlet: The Texts of 1603 and 1623", The Arden Shakespeare Third Series, 2006 at p.73.

- ^ Othello 1.3.245

- ^ Honigmann & Thompson 2016, p. 349-350.

- ^ a b c d e Neill 2008, p. 405.

- ^ Othello 3.3.456-463.

- ^ Othello 4.3.29-52 and 4.3.54-56.

- ^ Neill 2008, pp. 405, 411.

- ^ Honigmann & Thompson 2016, p. 358.

- ^ Mowat and Werstine, 2017, p.xlix.

- ^ a b Neill 2008, p. 411.

- ^ Neill 2008, p. 412.

- ^ a b Neill 2008, p. 413.

- ^ Neill 2008, pp. 414–415.

- ^ Neill 2008, p. 414.

- ^ Neill 2008, pp. 416–417.

- ^ Neill 2008, p. 430.

- ^ Othello 3.3.167-169.

- ^ Desmet, Christy "Character Criticism" in Wells, Stanley and Orlin, Lena Cowen "Shakespeare: An Oxford Guide", Oxford University Press, 2003, pp.351-372 at p.357, citing A. C. Bradley's Shakespearean Tragedy.

- ^ Muir 1996, pp. 21–22.

- ^ Muir 1996, p. 22.

- ^ Muir 1996, p. 20.

- ^ Muir 1996, p. 23.

- ^ Muir 1996, p. 24.

- ^ Muir 1996, p. 38.

- ^ Ben Okri's A Way of Being Free in Neill 2008, p. 113

- ^ Neill 2008, p. 146.

- ^ Neill 2008, p. 41.

- ^ Bartels, 2003, p.160.

- ^ Muir & McAlindon 2015, p. xxii.

- ^ Muir & McAlindon 2015, p. lxxii.

- ^ Singh, Jyotsna "Post-Colonial Criticism" in Wells, Stanley and Orlin, Lena Cowen "Shakespeare: An Oxford Guide", Oxford University Press, 2003, pp.492-507 at p.493.

- ^ Neill 2008, p. 45.

- ^ Othello 1.1.65.

- ^ Othello 1.1.87-88.

- ^ Othello 1.1.109-110.

- ^ Othello 1.2.70-71.

- ^ Othello 3.3.267.

- ^ Othello 3.3.390-391.

- ^ Mowat and Werstine, 2017, p.267.

- ^ "Moor". Oxford English Dictionary (Online ed.). Oxford University Press. doi:10.1093/OED/2172406316. (Subscription or participating institution membership required.)

- ^ Bartels, Emily C (2003). "Shakespeare's view of the world". In Wells, Stanley; Cowen Orlin, Lena (eds.). Shakespeare: an Oxford guide. Oxford: Oxford University Press. pp. 151–164. doi:10.1093/oso/9780199245222.003.0014. ISBN 978-0-19-924522-2. Retrieved 9 September 2024.

- ^ Honigmann & Thompson 2016, p. 25.

- ^ Virginia Mason Vaughan's "Othello: A Contextual History" in Neill 2008, pp. 122–123. The quotation is a parody of Othello 3.3.387-388.

- ^ Ferraro, Bruno (translator) Gli Hecatommithi - Third Decade, Seventh Novella in Neill 2008, p. 434-444

- ^ Honigmann 1997, p. 60.

- ^ Honingmann, 1997, p.29, citing Thomas Rymer's A Short View of Tragedy.

- ^ Neill 2008, p. 3.

- ^ Lamb, Charles and Lamb, Mary "Tales from Shakespeare", 1807, Penguin Popular Classics edition, 1995, p.281.

- ^ Singh, 2003, p.494.

- ^ Samuel Taylor Coleridge's Lectures and Notes on Shakespeare and Other English Poets quoted in Honigmann & Thompson 2016, pp. 29–31

- ^ Honigmann & Thompson 2016, p. 32.

- ^ Neill 2008, p. 120.

- ^ Martin Orkin's "Othello and the "Plain Face" of Racism" in Neill 2008, p. 120

- ^ Honigmann & Thompson 2016, pp. 62–63.

- ^ a b Honigmann & Thompson 2016, p. 63.

- ^ Ben Okri's A Way of Being Free quoted in Honigmann & Thompson 2016, pp. 63

- ^ Honigmann & Thompson 2016, p. 65.

- ^ Hugh Quarshie's lecture Hesitations on Othello in Neill 2008, p. 69-70

- ^ Honigmann & Thompson 2016, pp. 65–66, 87–89.

- ^ Mowat and Werstine, 2017, p.335, citing Virginia Vaughan's 2005 "Performing Blackness on English Stages 1500-1800".

- ^ "Othello". Walters Art Museum.

- ^ Othello 1.1.169-171.

- ^ Green MacDonald, Joyce "Black Ram, White Ewe: Shakespeare, Race, and Women" in Callaghan, Dympna (ed.) "A Feminist Companion to Shakespeare" Blackwell Publishers Limited, 2001, pp.188-207 at p.188 & 192

- ^ Muir & McAlindon 2015, p. xxv.

- ^ Othello 5.2.139-142.

- ^ Snyder, Susan, "Othello: A Modern Perspective" in Mowat, Barbara A (ed.), Werstine, Paul (ed.) and Shakespeare, William, "Othello", Folger Shakespeare Library edition, Simon and Schuster, 2017, pp.291-302 at p.299.

- ^ Snyder, 2017, pp.299-300.

- ^ Stanton, Kay ""Made to write 'whore' upon?": Male and Female Use of the Word "Whore" in Shakespeare's Canon" in Callaghan, Dympna (ed.) "A Feminist Companion to Shakespeare" Blackwell Publishers Limited, 2001, pp.80-102 at pp.94 & 95.

- ^ Stanton, 2001, p.97

- ^ Stanton, 2001, p.98.

- ^ Howard, Jean E. "Feminist Criticism" in Wells, Stanley and Orlin, Lena Cowen "Shakespeare: An Oxford Guide", Oxford University Press, 2003, pp.411-430 at p.427, in turn citing Lisa Jardine's essay "She sat like Patience on a Monument / Smiling at grief".

- ^ Muir & McAlindon 2015, p. lv.

- ^ Bate & Rasmussen 2009, p. 188.

- ^ Othello 5.2.192-194, 5.2.217-220 and 5.2.222.

- ^ Neill 2008, p. 176.

- ^ Neill 2008, p. 4.

- ^ Orlin, Lena Cowen "Introduction" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.1-16 at p. 5.

- ^ Green MacDonald, 2001, pp.193-194

- ^ Othello 3.4.57-77.

- ^ Watts, Cedric "Othello's Magical Handkerchief" in Sutherland, John and Watts, Cedric (eds.) "Henry V, War Criminal? & Other Shakespeare Puzzles" Oxford World's Classics series, Oxford University Press, 2000, pp.76-84 at pp.78-79

- ^ Honigmann & Thompson 2016, pp. 50–51.

- ^ Othello 3.4.57-60

- ^ Othello 5.2.214-215.

- ^ Watts, 2000, p.80. Smith, 2014, p.102.

- ^ Honigmann & Thompson 2016, p. 50.

- ^ Honigmann 1997, p. 72.

- ^ Othello 3.3.290-292.

- ^ Howard, 2003, p.425.

- ^ Smith, Ian "Othello's Black Handkerchief" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.95-120 at p.95.

- ^ Howard, 2003, p.426

- ^ Neill 2008, p. 155.

- ^ Honigmann & Thompson 2016, p. 51.

- ^ Othello 3.4.76.

- ^ Smith, 2014, pp.102 & 105.

- ^ Rosenfeld, Colleen Ruth "Shakespeare's Nobody" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.257-279 at p.269.

- ^ Hornback, Robert "'Speak[ing] Parrot' and Ovidian Echoes in Othello: Recontextualizing Black Speech in the Global Renaissance" in Orlin, Lena Cowen (ed.) "Othello - The State of Play" The Arden Shakespeare, Bloomsbury Publishing, 2014, pp.63-93 at p.86. Henry V is in fourth place.

- ^ A Midsummer Night's Dream Act 1 Scene 1 Lines 36-38.

- ^ Othello 1.3.179-180

- ^ Honigmann & Thompson 2016, pp. 10–11.

- ^ Mowat, Barbara A (ed.), Werstine, Paul (ed.) and Shakespeare, William, "Othello", Folger Shakespeare Library edition, Simon and Schuster, 2017, p.xxii.

- ^ Watson, Robert N. "Tragedy" in Braunmuller, A. R. and Hattaway, Michael (eds.) "The Cambridge Companion to English Renaissance Drama" Second Edition, Cambridge University Press, 2003, pp.292-343 at p.329.

- ^ Honigmann 1997, p. 34.

- ^ Othello 1.1.5-7, 1.1.32, 1.1.87-90 & 1.1.108-112

- ^ Honigmann 1997, p. 35.

- ^ a b Neill 2008, p. 31.

- ^ Othello 1.1.7-32.

- ^ a b Muir & McAlindon 2015, p. xliii.

- ^ Othello 1.3.385-9 & 2.1.293-297.

- ^ Honigmann & Thompson 2016, p. 45.

- ^ Othello 2.1.303-305.

- ^ Muir & McAlindon 2015, pp. xliii–xliv.

- ^ Othello 2.1.289-291

- ^ Othello 5.1.18-20.

- ^ Muir & McAlindon 2015, p. xliv.

- ^ Samuel Taylor Coleridge's marginal note to the closing speech of Act 1 in his own personal copy of Othello, cited by Honigmann & Thompson 2016, p. 45; Neill 2008, p. 31; Muir & McAlindon 2015, p. xliv and by Honigmann 1997, pp. 33–34

- ^ Honigmann 1997, pp. 50–51.

- ^ Watson, 2003, p.329.

- ^ Othello 5.2.300-301

- ^ Watson, 2003, p.331.

- ^ Orgel, Stephen "Introduction" in Sutherland, John and Watts, Cedric (eds.) "Henry V, War Criminal? & Other Shakespeare Puzzles" Oxford World's Classics series, Oxford University Press, 2000, pp.ix-xvi at p.xi.

- ^ a b Orgel, 2000, p.xi.

- ^ Orgel, 2000, p.xii.

- ^ Honigmann 1997, p. 69 citing M. R. Ridley's Arden Second Series edition of the play.

- ^ Othello 5.2.209-210.

- ^ Othello 3.3.296.

- ^ Othello 3.4.173.

- ^ Muir 1996, p. 26.

- ^ Othello 1.3.380.

- ^ Othello 4.2.187-188.

- ^ a b Honigmann 1997, p. 70.

- ^ Othello 3.4.23.

- ^ a b Honigmann 1997, p. 68.

- ^ Bate & Rasmussen 2009, p. 189.

- ^ Neill 2008, p. 35.

- ^ Neill 2008, p. 36.

- ^ a b c Honigmann & Thompson 2016, p. 67.

- ^ Honigmann & Thompson 2016, p. 28.

- ^ Taylor, Gary "Shakespeare Plays on Renaissance Stages" in Wells, Stanley and Stanton, Sarah (eds.) "The Cambridge Companion to Shakespeare on Stage", Cambridge University Press, 2002, pp. 1–20 at p. 4.

- ^ Gurr, Andrew and Ichikawa, Mariko "Oxford Shakespeare Topics: Staging in Shakespeare's Theatres" Oxford University Press, 2000, p. 55.

- ^ Taylor, 2002, p. 5.

- ^ Bate and Rasmussen, 2009, p.149.

- ^ Marsden, Jean I "Improving Shakespeare: from the Restoration to Garrick" in Wells, Stanley and Siddons, Sarah (eds.) "The Cambridge Companion to Shakespeare on Stage", Cambridge University Press, 2002, pp. 21–36, at p. 21.

- ^ Brown, John Russell "The Oxford Illustrated History of the Theatre", Oxford University Press, 1995, pp. 206–207.

- ^ Gay, Penny "Women and Shakespearean Performance" in Wells, Stanley and Stanton, Sarah (eds.) "The Cambridge Companion to Shakespeare on Stage" Cambridge University Press, 2002, pp. 155–173, at p. 157.

- ^ Honigmann & Thompson 2016, p. 68.

- ^ Marsden, p. 21. For examples see Wikipedia's articles on The Tempest, Macbeth and King Lear.

- ^ Honigmann 1997, p. 90.

- ^ Honigmann 1997, pp. 90–92.

- ^ Muir & McAlindon 2015, pp. lxvi–lxvii.

- ^ John Bernard in The Theatrical Review (1772) cited by McAlindon, 2005, p.lxvii.

- ^ Morrison, Michael A. "Shakespeare in North America" in Wells, Stanley and Stanton, Sarah (eds.) "The Cambridge Companion to Shakespeare on Stage", Cambridge University Press, 2002, pp. 230–258, at pp. 231-232.

- ^ Stone, John (March 2024). "Othello Goes to Lisbon, 1765". Notes and Queries. https://doi.org/10.1093/notesj/gjae022

- ^ Honigmann & Thompson 2016, pp. 77–78.

- ^ Honigmann & Thompson 2016, pp. 78–79.

- ^ Neill 2008, p. 8.

- ^ Gillies, John "Stanislavski, Othello, and the Motives of Eloquence" in Hodgson, Barbara and Worthen, W. B. (eds.) "A Companion to Shakespeare and Performance", Blackwell Publishing Limited 2008, pp. 267–284, at p. 267.